# E363

## PROPOSAL FOR EXPERIMENT AT RCNP

July 12, 2010

#### TITLE:

# SER Measurement for Soft-error Hardened Circuits on a 65nm LSI

### SPOKESPERSON:

| Full Name         | Kazutoshi Kobayashi                                             |  |

|-------------------|-----------------------------------------------------------------|--|

| Institution       | Department of Electronics, Graduate School of Science and Tech- |  |

|                   | nology, Kyoto Institute of Technology                           |  |

| Title or Position | Professor                                                       |  |

| Address           | Matsugasaki, Sakyo, Kyoto, 606-8585                             |  |

| Phone number      | +81-75-724-7452                                                 |  |

| FAX number        | +81-75-724-7452                                                 |  |

| E-mail            | kobayasi@kit.ac.jp                                              |  |

## **EXPERIMENTAL GROUP:**

| K. Kobayashi | Graduate School of Sci. & Tech., Kyoto | Professor             |

|--------------|----------------------------------------|-----------------------|

|              | Institute of Technology                |                       |

| M. Hashimoto | Graduate School of Info. Sci. & Tech., | Associate Professor   |

|              | Osaka Univ.                            |                       |

| Y. Mitsuyama | Graduate School of Eng., Osaka Univ.   | Assistant Professor   |

| J. Furuta    | Graduate School of Informatics, Kyoto  | Graduate Student(M2)  |

|              | University                             |                       |

| C. Hamanaka  | Graduate School of Sci. & Tech., Kyoto | Graduate Student(M2)  |

|              | Institute of Technology                |                       |

| R. Harada    | Graduate School of Info. Sci. & Tech., | Graduate Student (M2) |

|              | Osaka Univ.                            |                       |

| D. Kuroda    | Graduate School of Info. Sci. & Tech., | Graduate Student (M2) |

|              | Osaka Univ.                            |                       |

| R. Yamamoto  | Graduate School of Sci. & Tech., Kyoto | Graduate Student(M1)  |

|              | Institute of Technology                |                       |

| <b>RUNNING TIME:</b> | Installatio | on time without beam | .5 days(for each beam time) |

|----------------------|-------------|----------------------|-----------------------------|

|                      | Test runn   | ent .5 days          |                             |

| Data runs            |             |                      | 3 days                      |

| BEAM LINE:           |             |                      | RING Cyclotron : WN course  |

| BEAM REQUIREMENTS:   |             | Type of particle     | proton                      |

|                      |             | Beam energy          | $392 { m ~MeV}$             |

|                      |             | Beam intensity       | $\leq 1\mu A$               |

|                      |             |                      |                             |

| BUDGET: | Experimental expenses | 0 yen |

|---------|-----------------------|-------|

|---------|-----------------------|-------|

### TITLE: SER Measurement on a 65nm LSI

SPOKESPERSON: Kazutoshi Kobayashi

#### SUMMARY OF THE PROPOSAL

Soft errors on LSIs are categorized to SEU (Single Event Upset) and SET (Single Event Transient). Workstations for high reliability contains SRAMs with ECC but also FFs with some error resiliency for SEU.

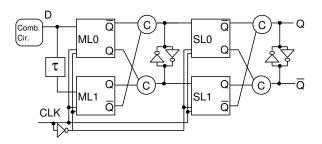

Figure 1 is the proposed dual-modular FF called Cross-coupled Dual Modular Redundancy Flip-Flop (BCDMR-FF)[1]. It is based on the well-known BISER structure[2]. In the BCDMR FF, C-elements are duplicated to prevent multiple latches to be flipped by an SET pulse from the C-element. BCDMR achieves same area and better power and delay at 0.5V compared with the BISER. It is mainly because its cross-coupled structure reduces the size of the C-element that must have enough strength to flip the weak keeper.

In December, 2009, we were going to confirm the vulnerability of the BCDMR-FF by the neutron irradiation at RCNP. But it was not successful since no clock signal was applied to the DUT. But  $\alpha$  particle irradiation was successfully done. The BCDMR-FF is 160x stronger than the conventional BISER FF at 160MHz clock frequency. We will have another neutron irradiation in July, 2010.

In this proposal, we explain the neutron irradiation measurement for a brand-new chip. It is an enhanced version of the first one already explained. We will implement these four circuit structures on a chip.

- 1. Shift Registers of custom layouts of the BCDMR and BISER FFs as in Fig. 2

- 2. Ring Oscillators to Measure Performance, Power and Variations

- 3. Minute and Long-ranged SET Pulse Capture Circuits

- 4. MCU Measurement and Well-Bias Capture Circuits

Figure 1: Bistable Cross-coupled DMR (BCDMR) FF. Figure 2: Custom layout cell of the BCDMR FF