# 200 $\mu\text{m}$ ピッチ 半導体ピクセル検出器 のための信号処理用2次元VLSIの開発

東京大学 理学系研究科 物理学専攻

ISAS/JAXA

蛭田 達朗

田村 健一、池田 博一、高島 健

中澤 知洋、高橋 忠幸 (ISAS/JAXA)

RCNP研究会

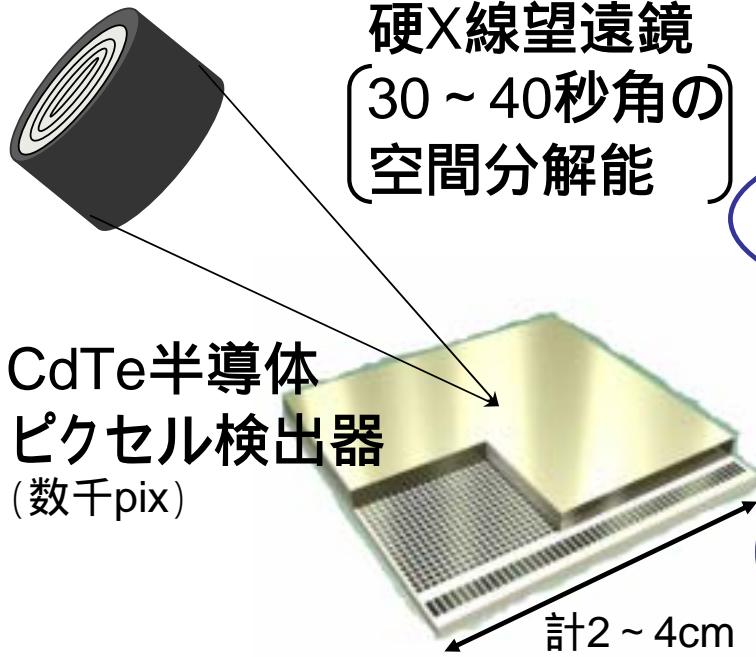

# 硬X線 高感度 分光撮像観測

## 必要な観測装置

### 目標とする2次元VLSI

アナログ性能

低ノイズ(  $1\text{keV}@100\text{keV}(\text{FWHM})$  )

$100\text{e-}(\text{ENC})$

2次元化

ピクセルサイズ( $200\mu\text{m}$ 角程度)

消費電力(  $250\mu\text{W}/\text{pixel}$  )

高速処理(  $<\text{数}10\mu\text{s}/\text{count}$  )

2次元アナログVLSI

これらの目標を達成したVLSIの開発は、ピクセル半導体

検出器実現の突破口となる

# 独自のアーキテクチャで 世界に類をみないVLSIを実現する

新たなアーキテクチャでいきなり目標とするVLSIを開発して、すぐに実現できるようなものではない

目標のVLSI実現のため、独自のアーキテクチャでの開発を積み重ねてきた

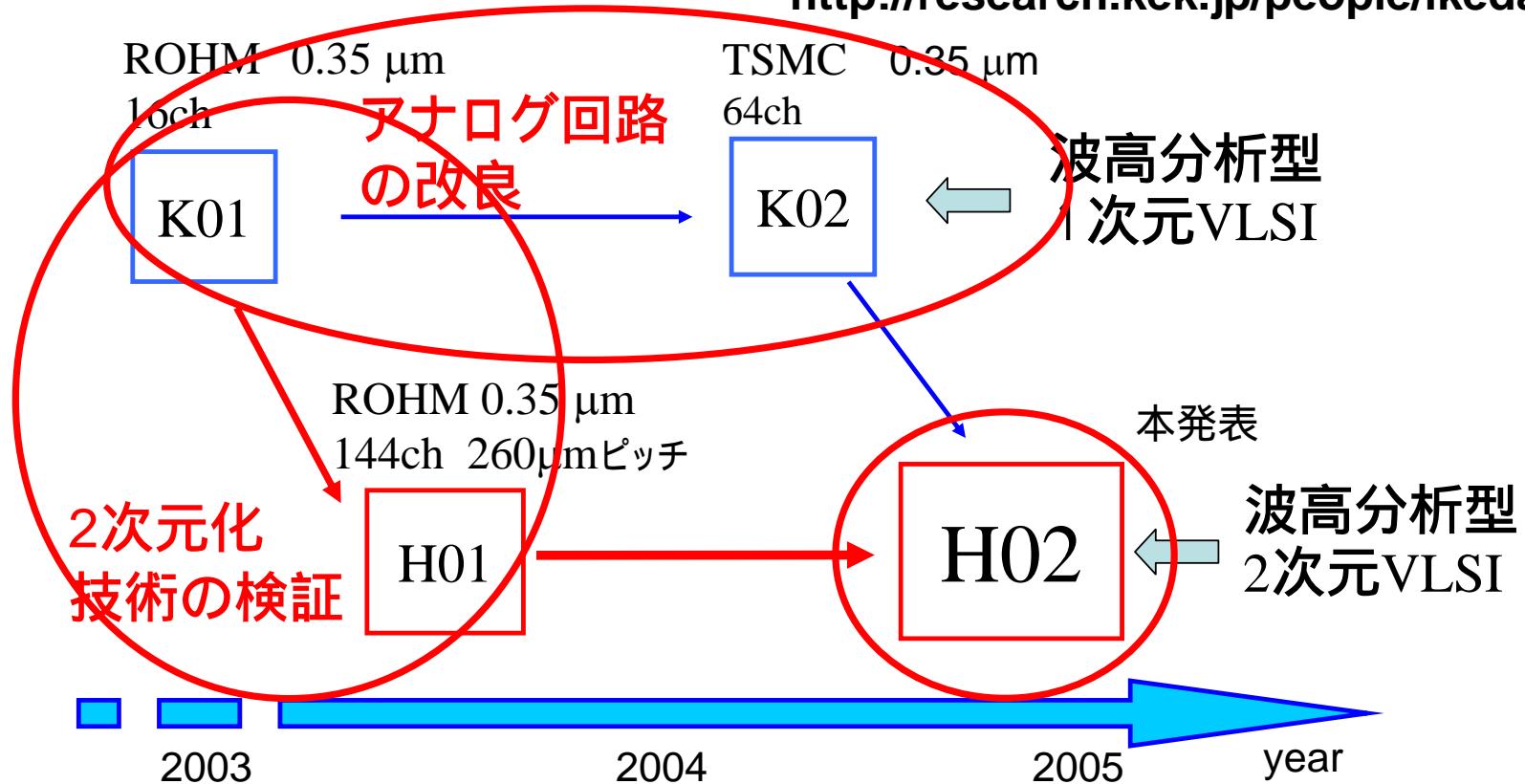

# アナログVLSI 開発の流れ ~OPEN IP プロジェクト

<http://research.kek.jp/people/ikeda/>

実用する第1ヴァージョンの2次元VLSI

「H02」

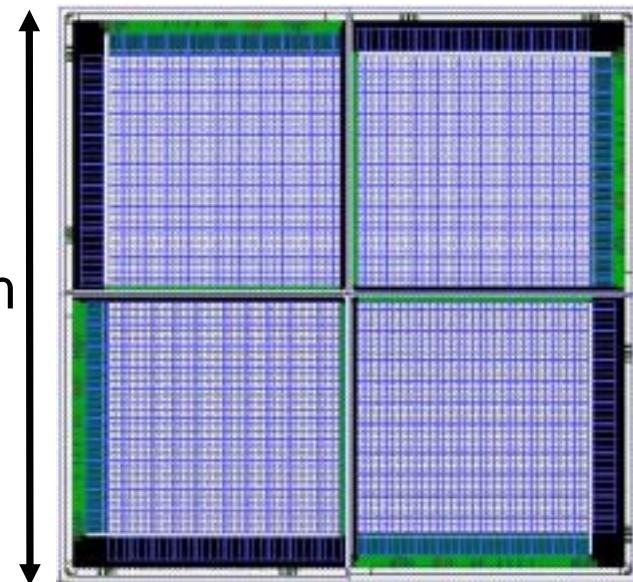

# 200 $\mu$ m ピッチ 2次元アナログVLSIの設計

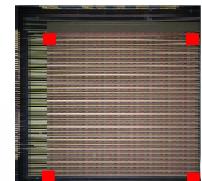

極めて大きいチップ

16mm

H02 レイアウト図

# 設計したアナログVLSIの仕様

|           |                                                                    |

|-----------|--------------------------------------------------------------------|

| ファウンダリ    | TSMC 0.25- $\mu$ m CMOS                                            |

| 入力電荷極性    | 正電荷                                                                |

| ピクセル数     | $64 \times 64 \text{ pix}$ ( $32 \times 32 \text{ pix} \times 4$ ) |

| チップサイズ    | 16 mm $\times$ 16 mm (8 mm $\times$ 8 mm)                          |

| ピクセルサイズ   | 200 $\mu$ m $\times$ 200 $\mu$ m                                   |

| 最大入力エネルギー | 22000 electron or 44000 electron                                   |

| 電源電圧      | $\pm 1.25\text{V}$                                                 |

| 消費電力      | 150 $\mu\text{W} / \text{pixel}$                                   |

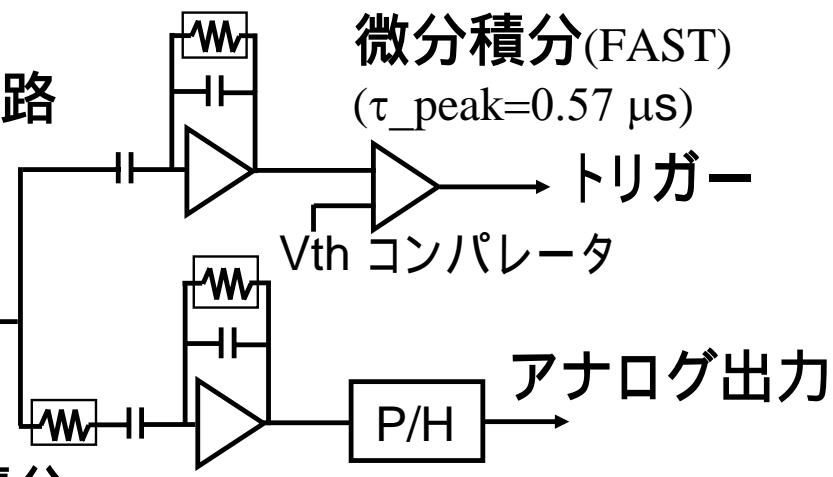

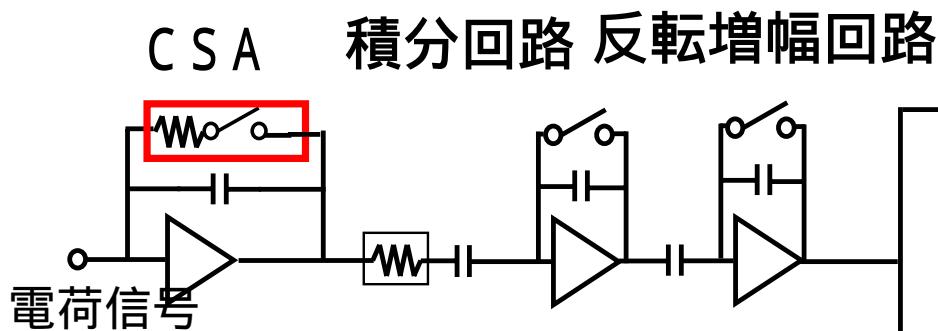

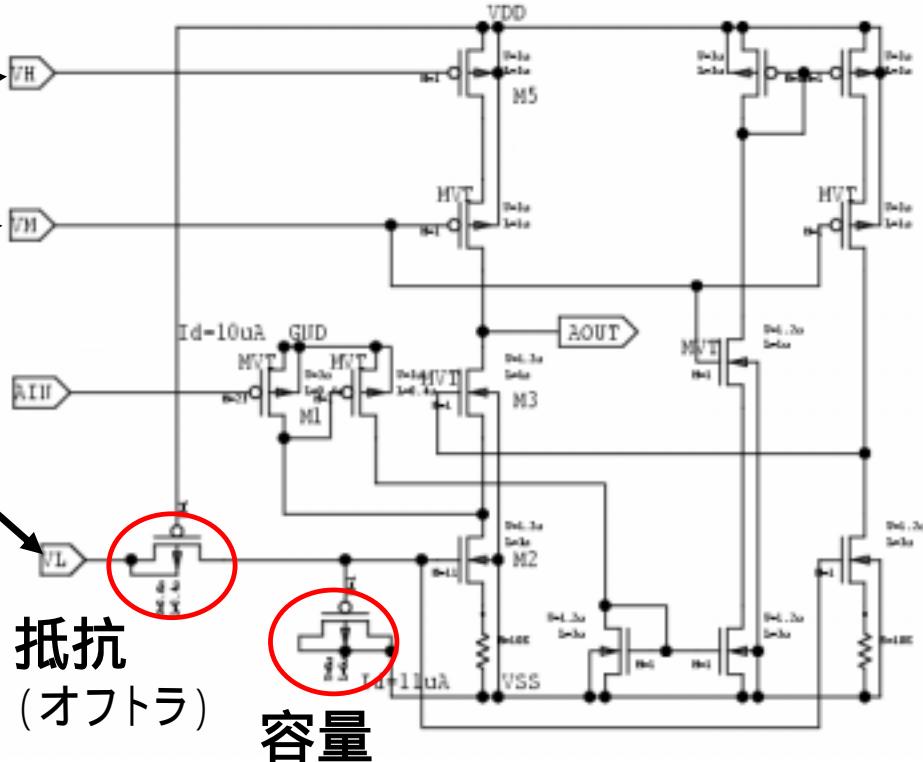

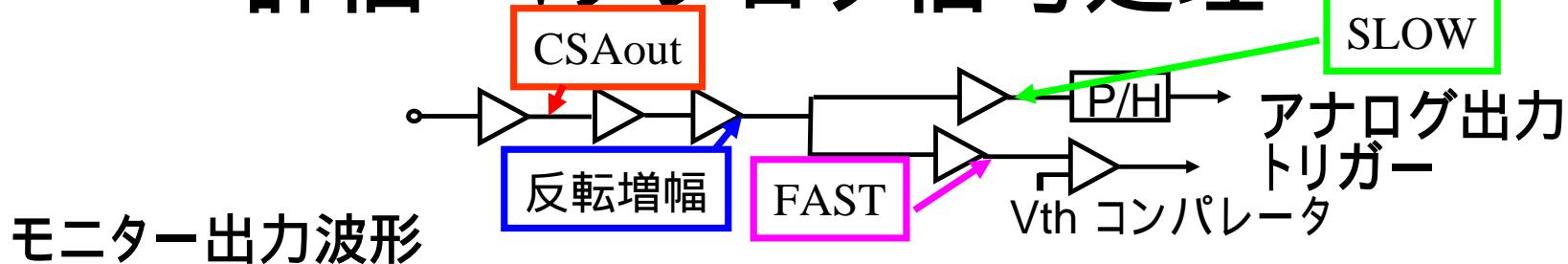

# 1ピクセル分のアナログ回路構成

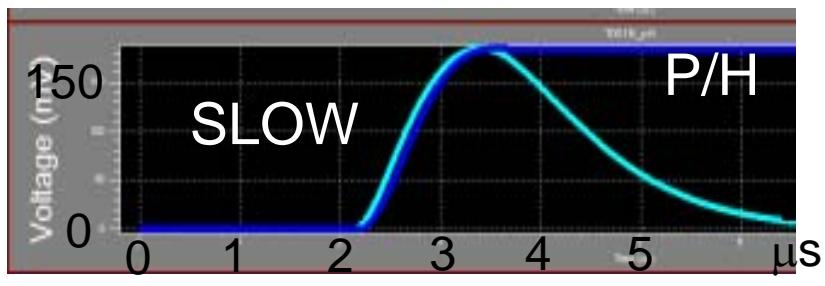

微分積分 (SLOW) ( $\tau_{peak}=1.39 \mu s$ )

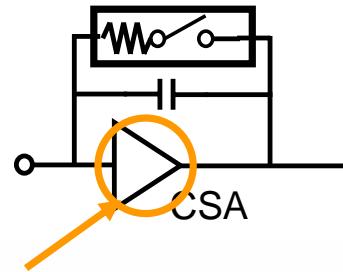

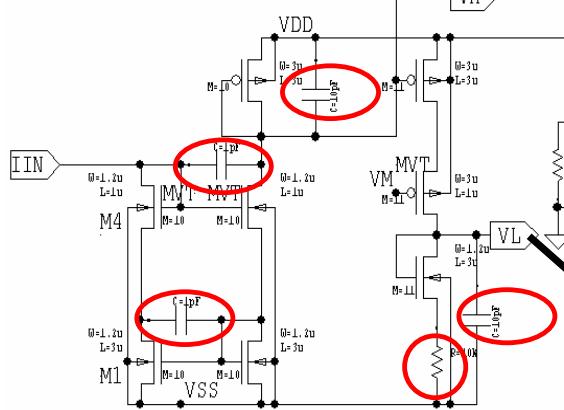

# 電源の揺れに対する感度の低減の工夫

(前回の試作チップでの問題点)

CSA用増幅器

BIAS回路

VH-VDD, VL-VSS間に

容量、抵抗を挿入

バイアス電圧の安定化

VL - VSS間に電源の揺れへの

感度の低減

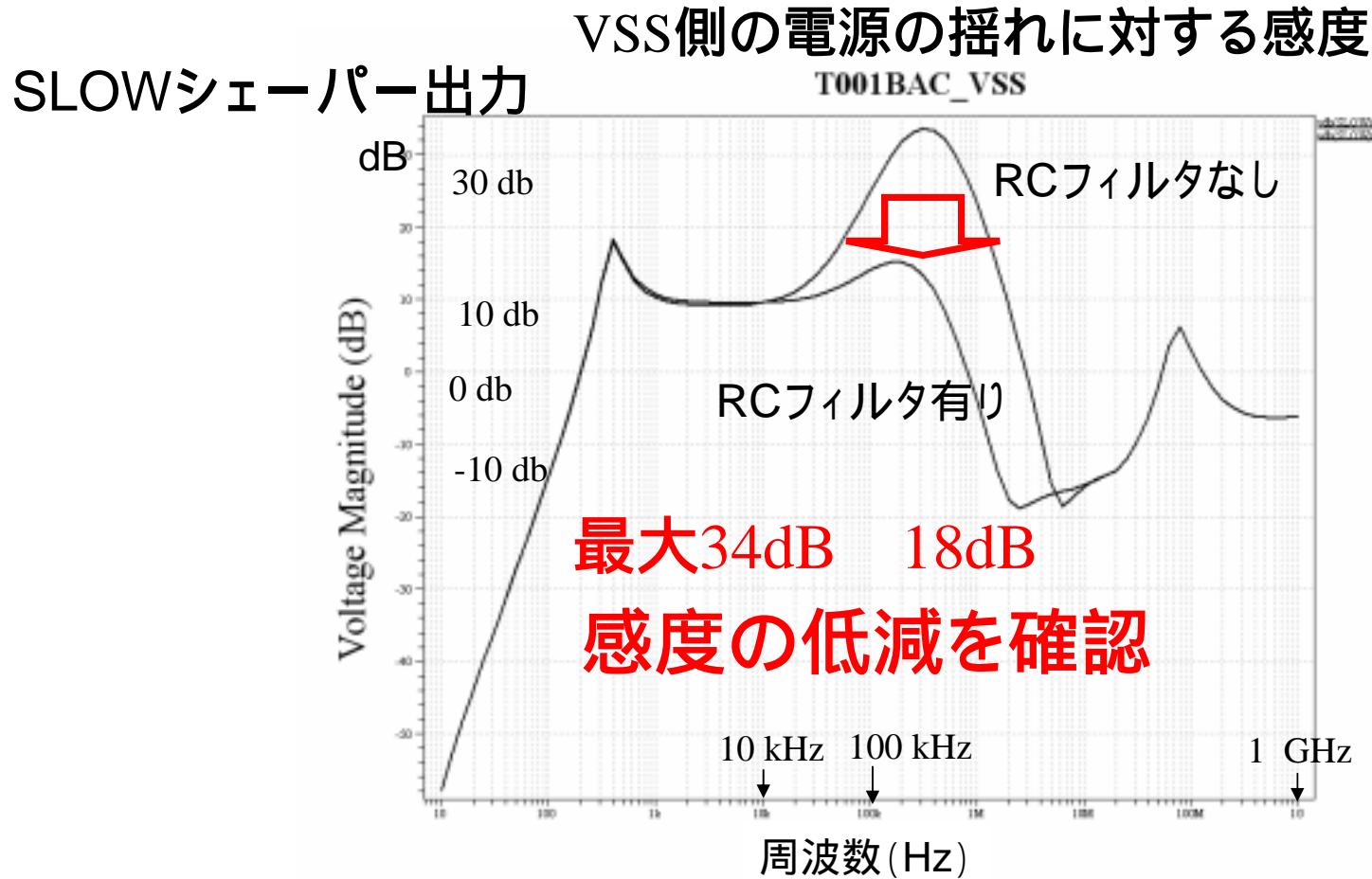

# 電源の揺れに対する感度の シミュレーション

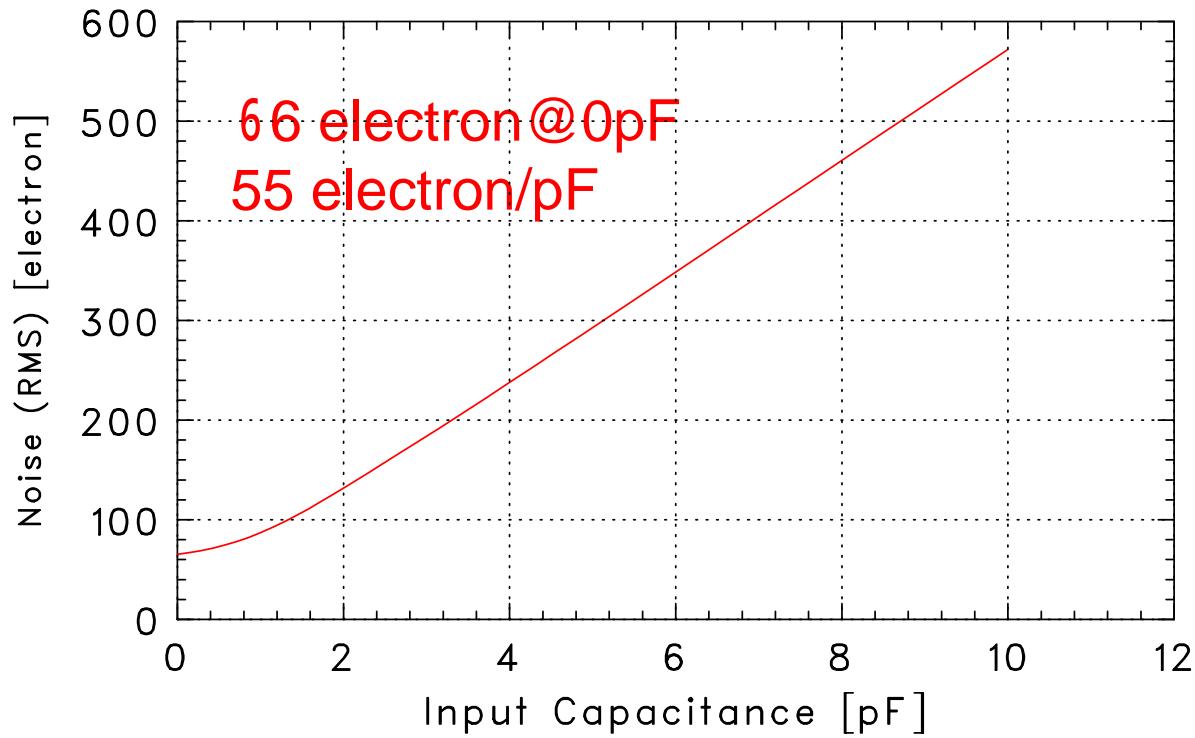

# ノイズレベルをシミュレーションで評価

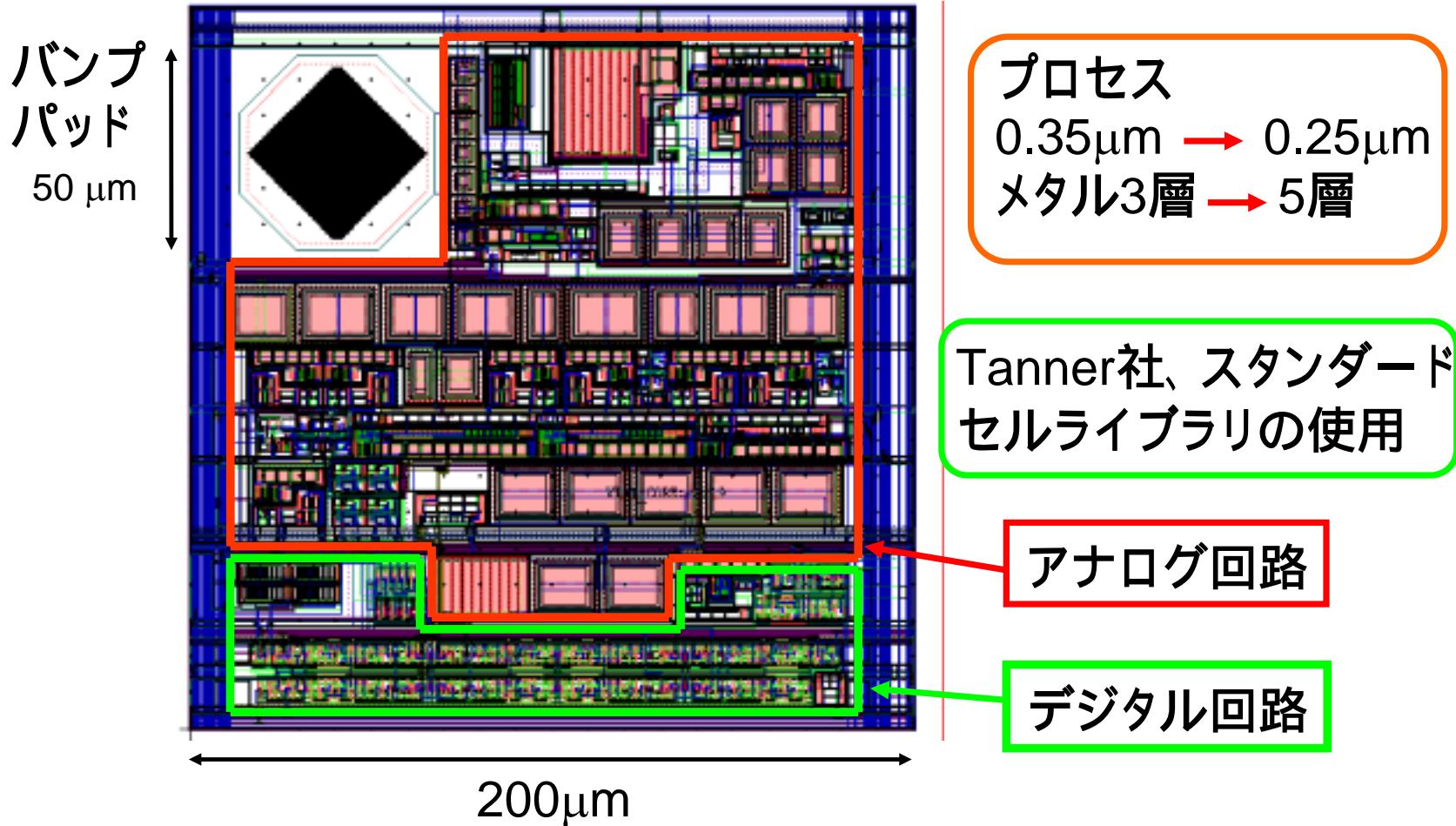

# 1ピクセル分のレイアウト～極小化の工夫

所要の回路を200  $\mu\text{m}$  角に収めることに成功

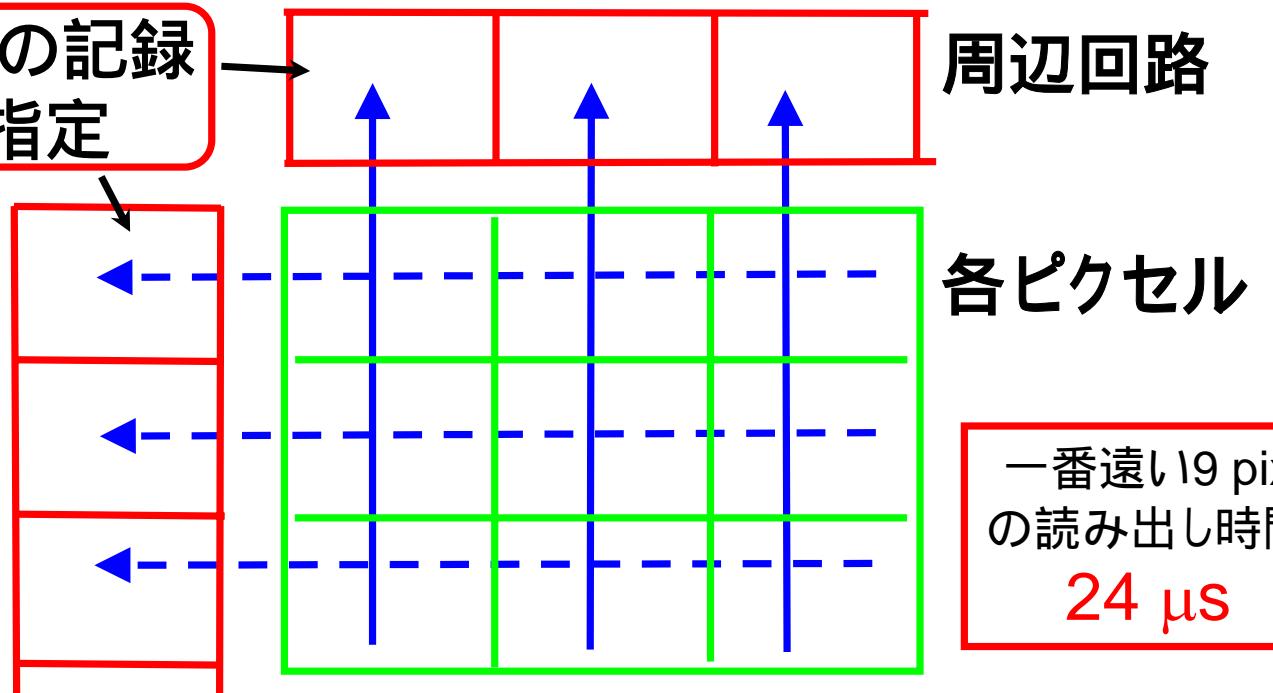

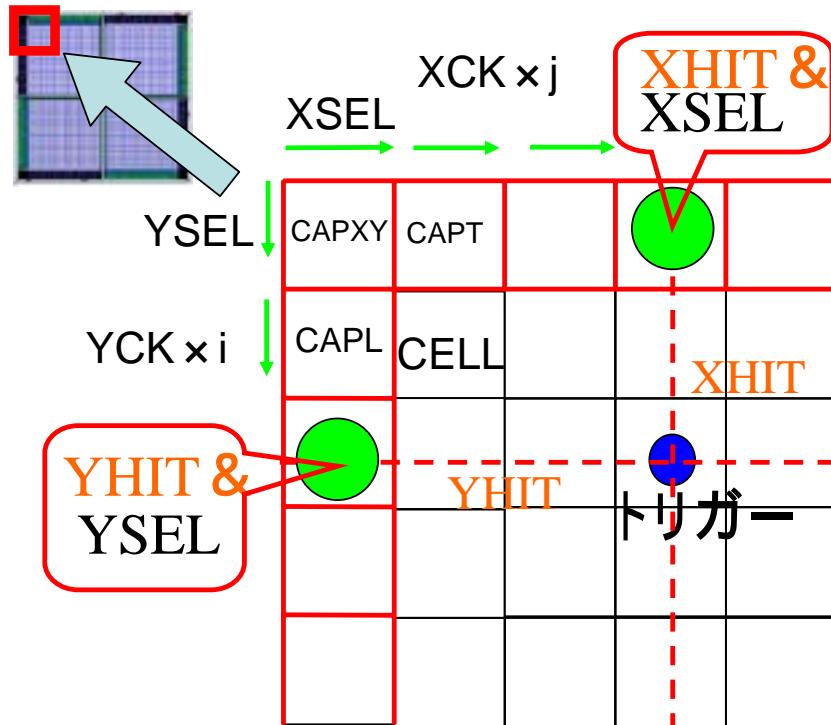

# 2次元読み出しシステム

周辺回路に配置したシフトレジスタを用いて、

ヒットパターンを読み出す (HIT情報と選択信号の論理積)

アドレス指定読み出しにより、任意のピクセルの

アナログ出力信号をAD変換する

HIT情報の記録

アドレス指定

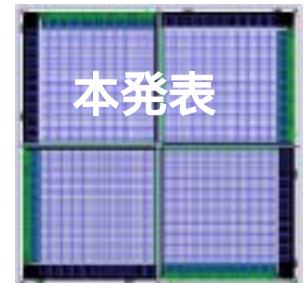

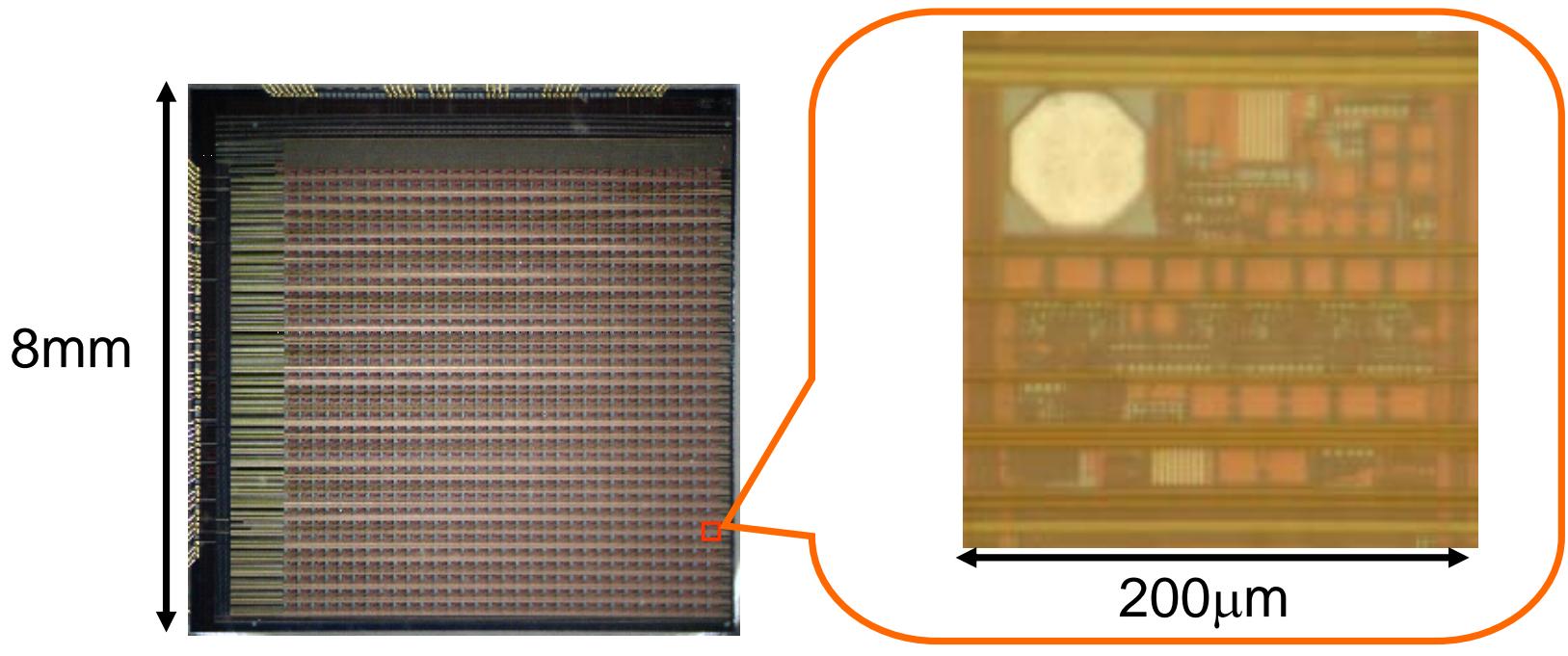

# 製作したアナログVLSI単体の初期評価

32 × 32ピクセルサブチップの写真

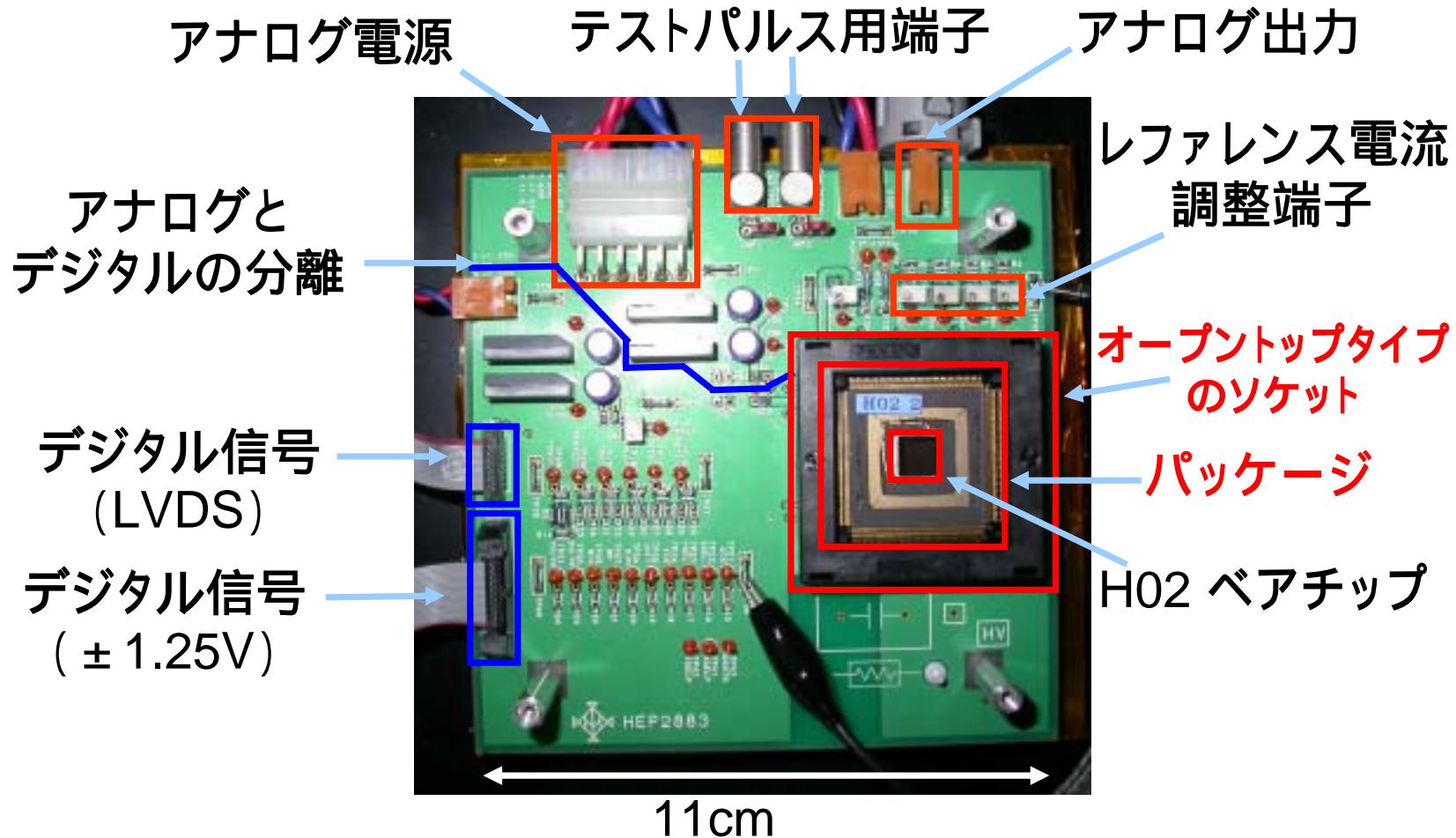

# H02専用の評価ボードを設計

# 評価

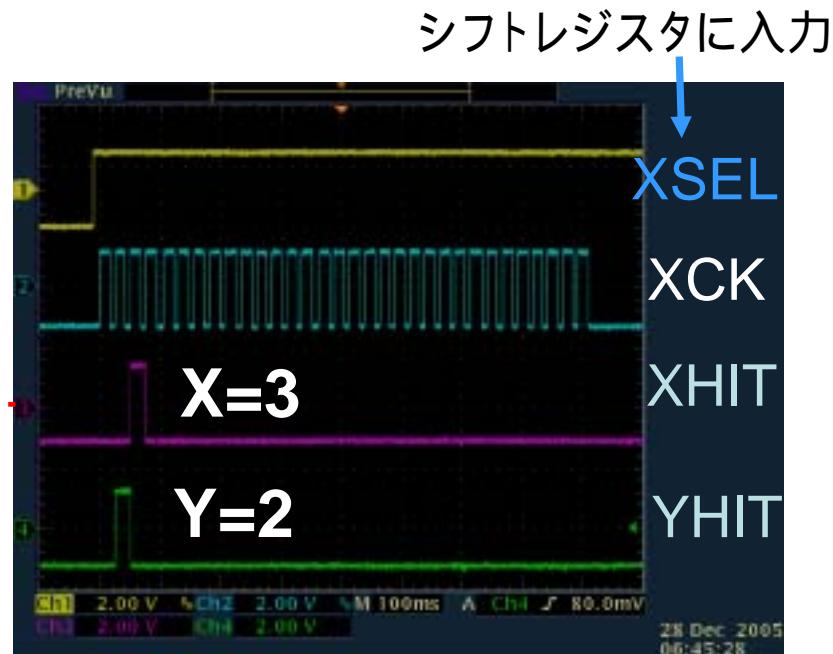

## :2次元読み出しシステムの動作確認

(3, 2)ピクセルからトリガーが

出力されたときのヒットパターン

ヒットパターンの読み出し、アドレス指定の動作を確認

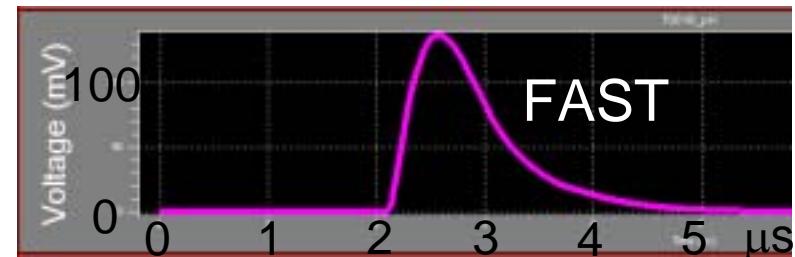

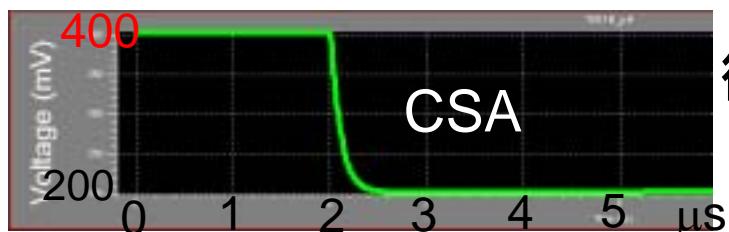

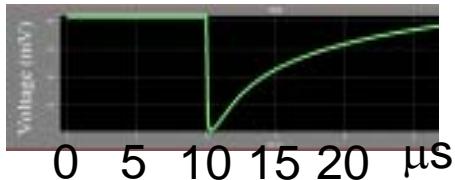

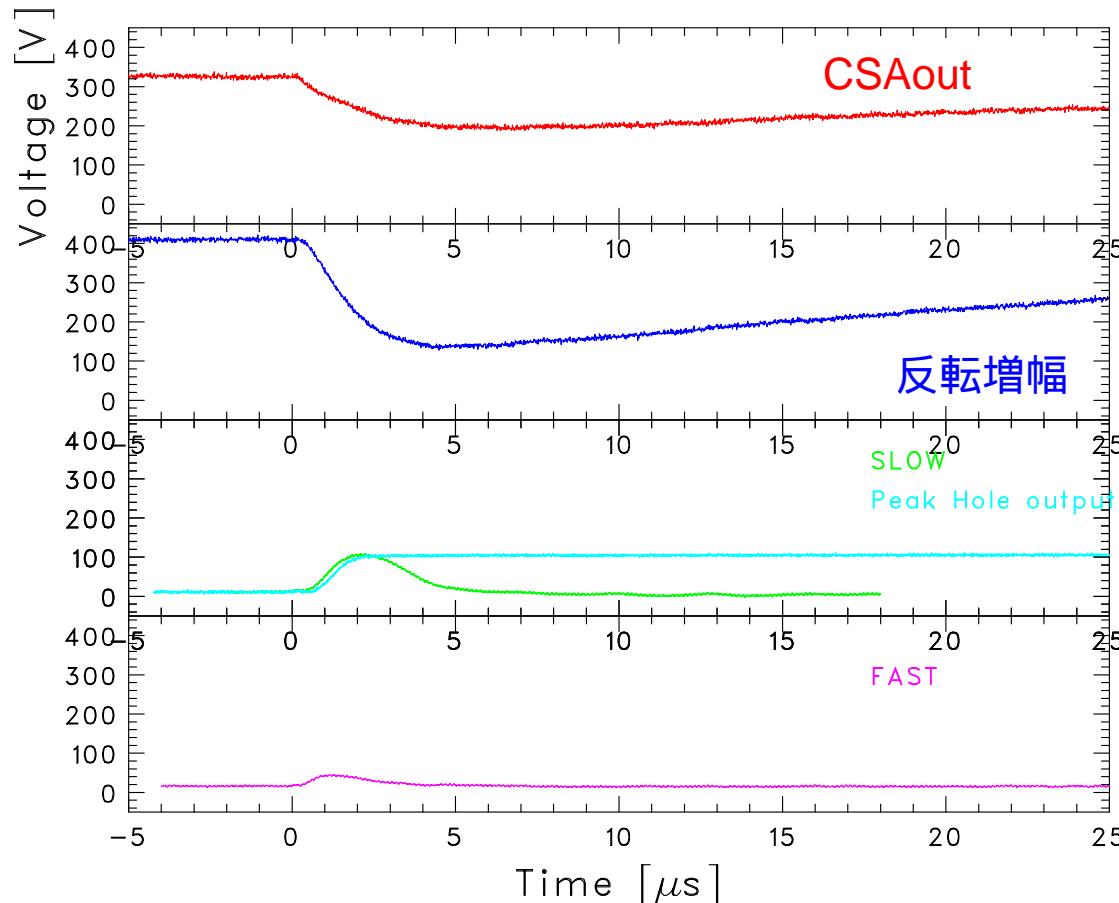

# 評価：アナログ信号処理

モニター出力波形

# 極小領域(200 $\mu\text{m}$ 角)に収められた 低雑音信号処理回路の動作を確認

## 問題点

一方、モニター出力波形がなまっており

1. CSAの出力波高が低い(半分程度)

長い配線(モニター出力、テストパルス)による

結合容量が原因の可能性

2. ライズタイムが長い

同じく、長い配線(モニター出力、テストパルス)による

浮遊容量が原因の可能性

現在、原因を究明中

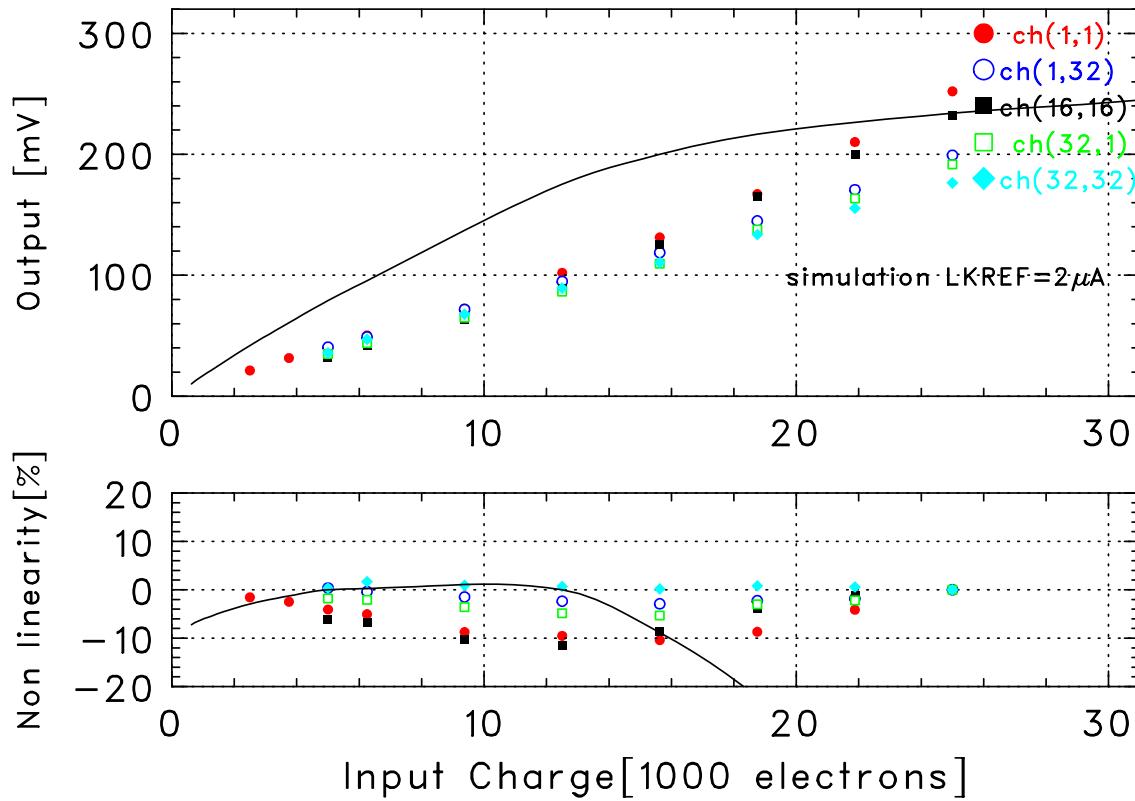

# 評価 リニアリティ

シミュレーションとの比較でダイナミックレンジが大きい

→ CSAの出力波高値の減少とコンシスティント

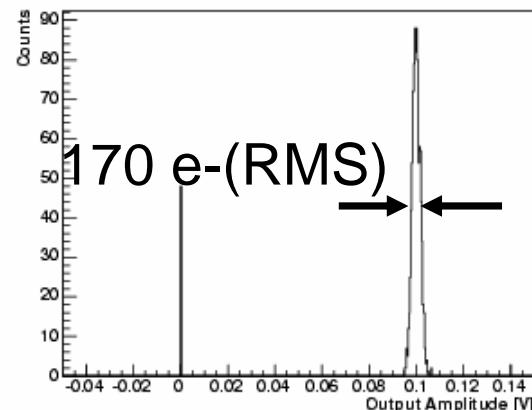

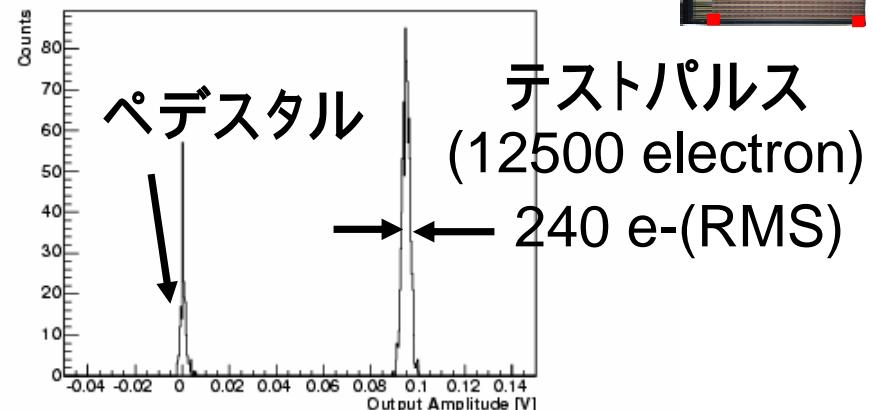

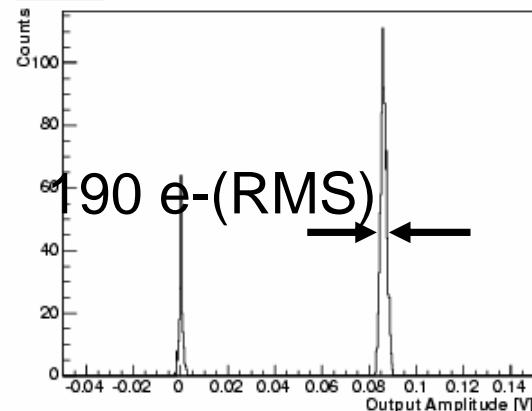

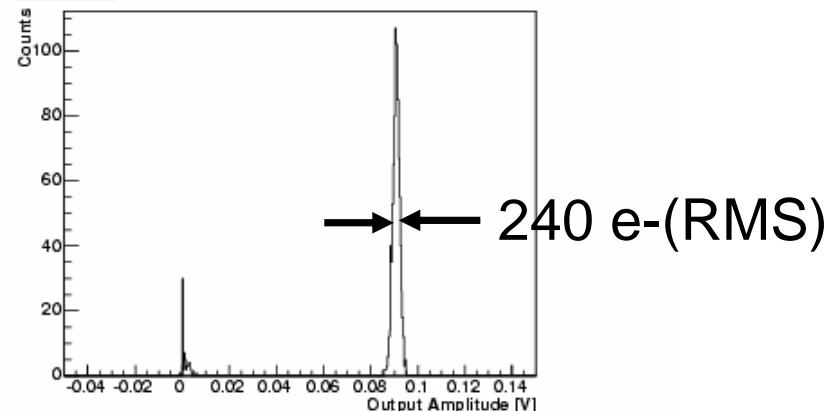

# 評価：ノイズレベルの評価結果

4隅のピクセルのテストパルスのスペクトルを取得

ch(1,1)

ch(1,32)

ch(32,1)

ch(32,32)

最良で170 electron のノイズレベルを達成

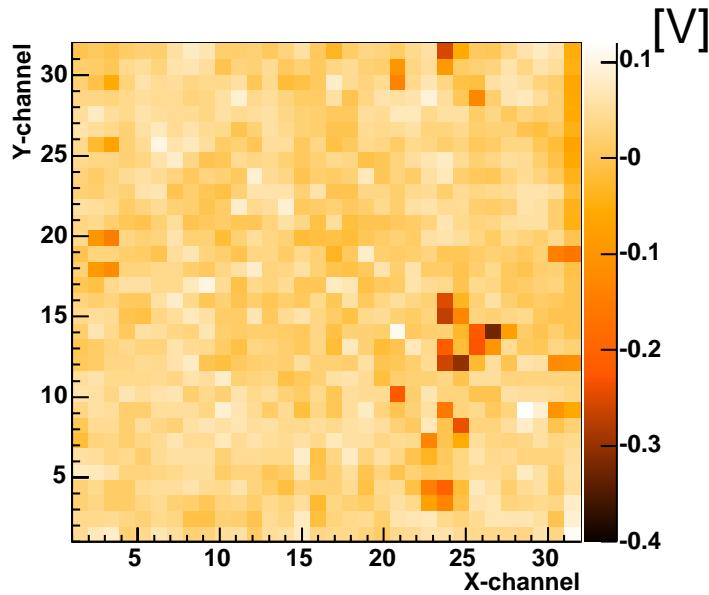

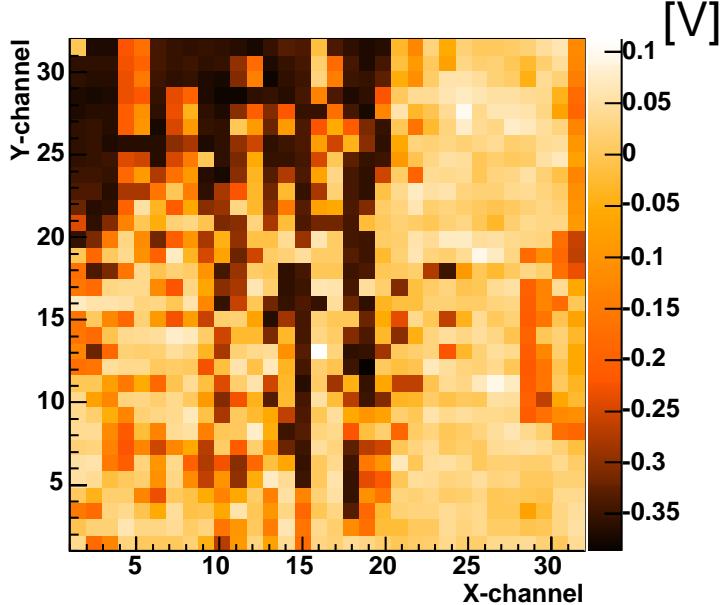

# 評価 : アナログ出力のペデスター

良品 粗悪品

H021\_180m\_later

H024\_180m\_later

異常ピクセル

35/1024

対角線及び4隅の34pixel全てから、

アナログ出力を確認

# まとめ

- 目標とする2次元アナログVLSIの実質的

第1ヴァージョンである200  $\mu\text{m}$ ピッチ 2次元 VLSI

「H02」を設計・開発

- 2次元読み出しシステムの動作を確認

- アナログ回路の出力波形を確認

- テストパルスのスペクトルを取得し、

170 electron のノイズレベルの結果を得た

- 95%以上のピクセルイールドを持つことが分かった

# 今後の課題

- CSAの帰還スイッチ(RST1)のダイナミック動作の確認

- CSAの出力波高値が低いことの原因の解明

- CSA出力のライズタイムが遅い原因の解明

- 上記2項目に対応して、モニター及び

アナログ出力をdisableにしたモードでの運用

- 全ピクセルに渡る統計的な調査

- 1素子の半導体検出器と接合した試験

- ピクセル半導体検出器と接合した試験